The AU8015EA is a low-noise (4.3 µVRMS), low-dropout linear regulator (LDO) capable of sourcing 4 A with only 200 mV of dropout. The device output voltage is pin-programmable from 0.8 V to 3.95 V and adjustable from 0.8 V to 5.15 V using an external resistor divider.

AU8015EA is the ideal choice to power noise-sensitive components found in high speed interfaces such as SERDES, 5G communication infrastructure such as High Speed ADCs, DACs and RF components due to its exceptional PSRR and low noise (4.3 µV RMS) characteristics. The high PSRR and low noise combination of AU8015EA limits power-supply induced phase noise and clock jitter.

The 5 V output capability of this device is well suited for RF amplifiers and RF front end. The AU8015EA device is also well suited for digital loads such as ASICs, FPGAs, and DSPs that require a low-input voltage and low-output voltage to minimize power dissipation while providing excellent transient performance that caters to current steps in digital loads due to clock domain switching, dynamic power and frequency scaling. The soft-start capability minimizes in-rush current, thereby allowing for a smooth and reliable start-up at the system level.

• Low Dropout: 200 mV at 4 A

• 1% (max) Accuracy Over Line, Load, and Temperature

• Output Voltage Noise:

-4.3 μV RMS at 0.8 V Output

-7.6 μV RMS at 5.0 V Output

• Input Voltage Range:

-1.4 V to 6.5 V without BIAS

-1.1 V to 6.5 V with BIAS

• Two Output Voltage Modes:

-0.8 V to 5.15 V (Set by resistor divider)

-0.8 V to 3.95 V (Set via programming pins)

• Excellent PSRR of 32 dB at 1 MHz

• Excellent Load Transient Response

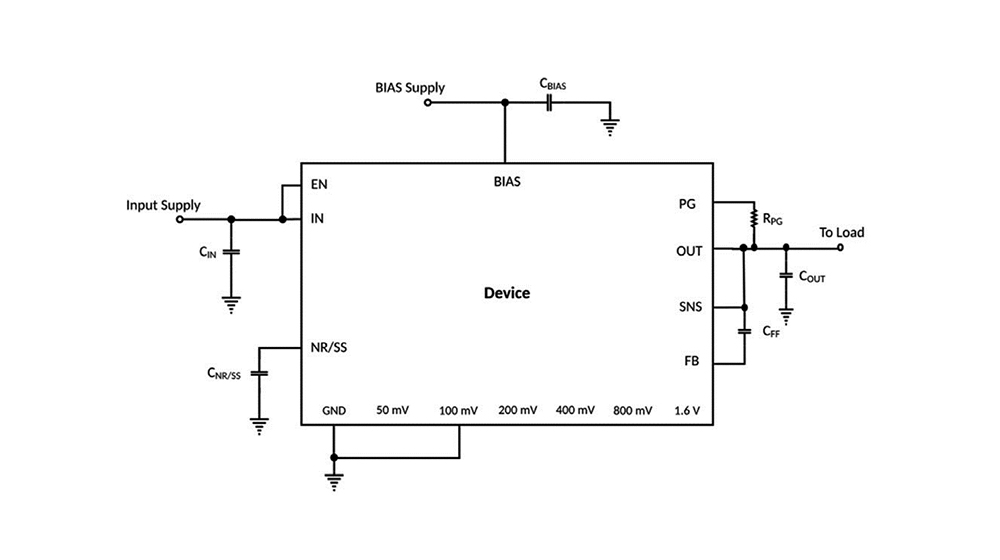

• Adjustable Soft-Start In-Rush Control

• 3.5 mm × 3.5 mm, 20-Pin, QFN

• 5G MIMO RF front end components

• Digital Loads: SerDes, FPGAs and DSPs

• High-speed Analog Circuits: VCO, ADC, DAC, and LVDS